# Registers and Memory

CSIM601251

Instructor: Tim Dosen DDAK

Slide By : Erdefi Rakun

Fasilkom UI

# Outline

- Register

- Memory

- Memory Unit

- Read/Write Operations

- Memory Arrays

*Note: These slides are taken from Aaron Tan's slide*

# Registers

- N-bit register:

- N flip-flops, possibly with added combinational gates that perform data-processing task

- Capable of storing n bits of binary information

- Counter:

- A register that goes through a predetermined sequence of states upon the application of clock pulse

- Register and Counter are sequential functional blocks that are used extensively in the design of digital systems

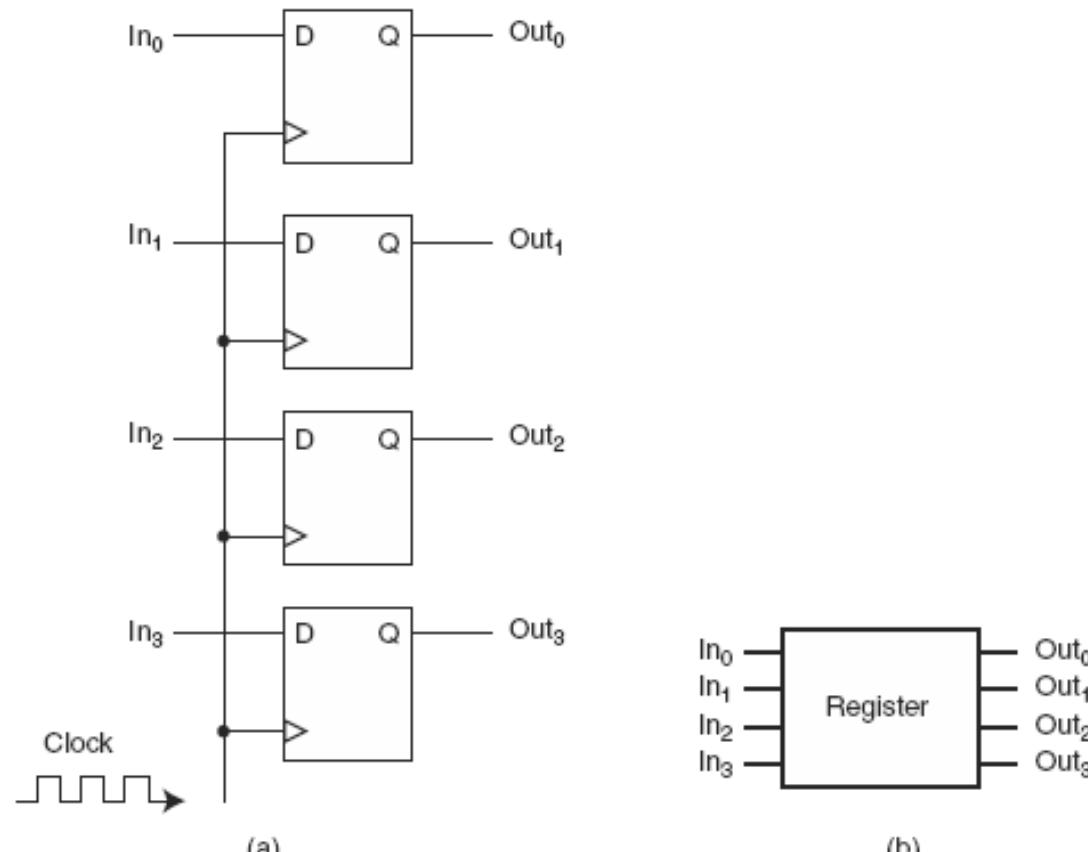

# D Flip-Flops Register

**FIGURE 3.23** a) A 4-Bit Register

b) A Block Diagram for a 4-Bit Register

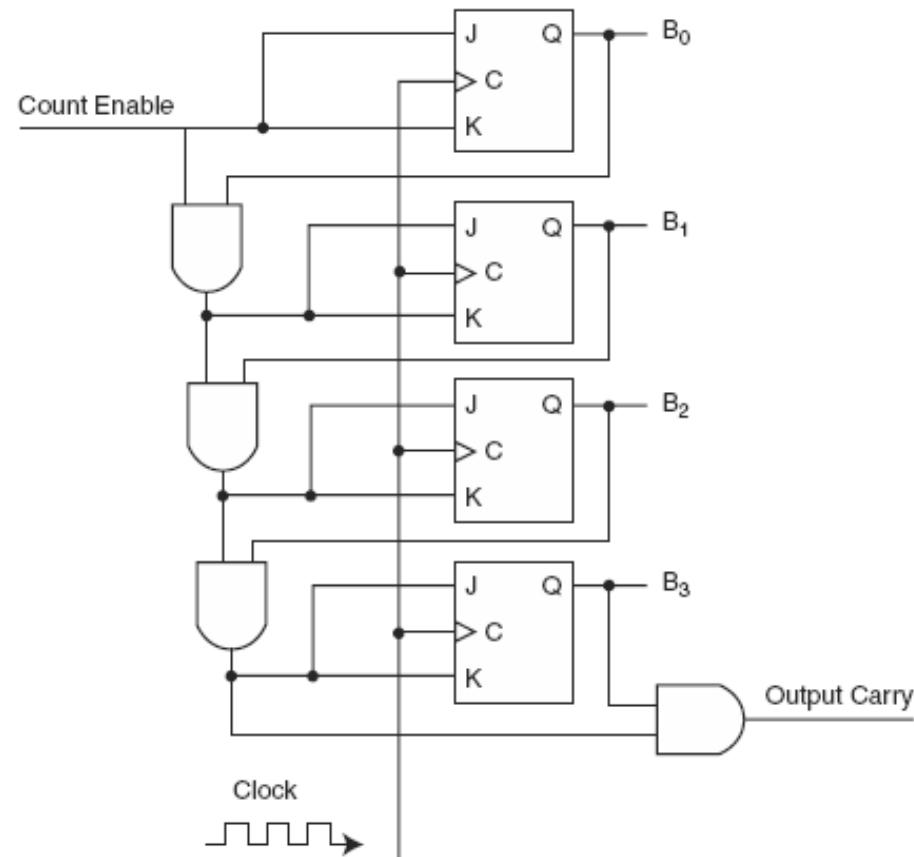

# Binary Counters

- Counters are sequential circuits that cycle through some states.

- They can be implemented using flip-flops.

- 0000, 0001, 0010, 0011.....

- Lower bit is complemented each time

- Whenever it changes state from 1 to 0, the bit to the left is complemented

- Each of the other bits changes state from 0 to 1 when all bit to the right are equal to 1

# JK Flip-Flops Counter

FIGURE 3.24 A 4-Bit Synchronous Counter Using JK Flip-Flops

# Outline

- Register

- Memory

- Memory Unit

- Read/Write Operations

- Memory Arrays

*Note: These slides are taken from Aaron Tan's slide*

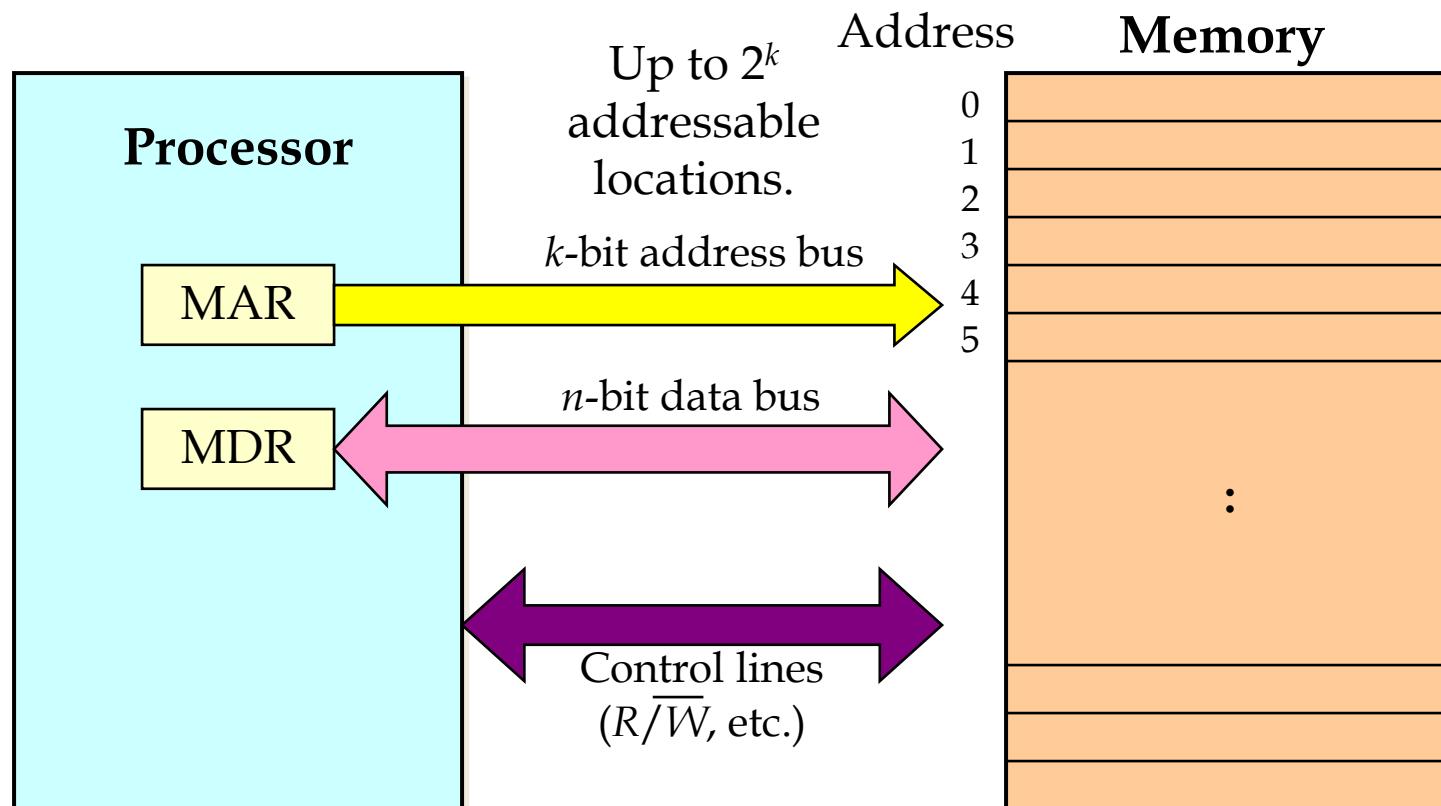

# Memory (1/4)

- Memory stores programs and data.

- Definitions:

- 1 byte = 8 bits

- 1 word: in multiple of bytes, a unit of transfer between main memory and registers, usually size of register.

- 1 KB (kilo-bytes) =  $2^{10}$  bytes; 1 MB (mega-bytes) =  $2^{20}$  bytes; 1 GB (giga-bytes) =  $2^{30}$  bytes; 1 TB (tera-bytes) =  $2^{40}$  bytes.

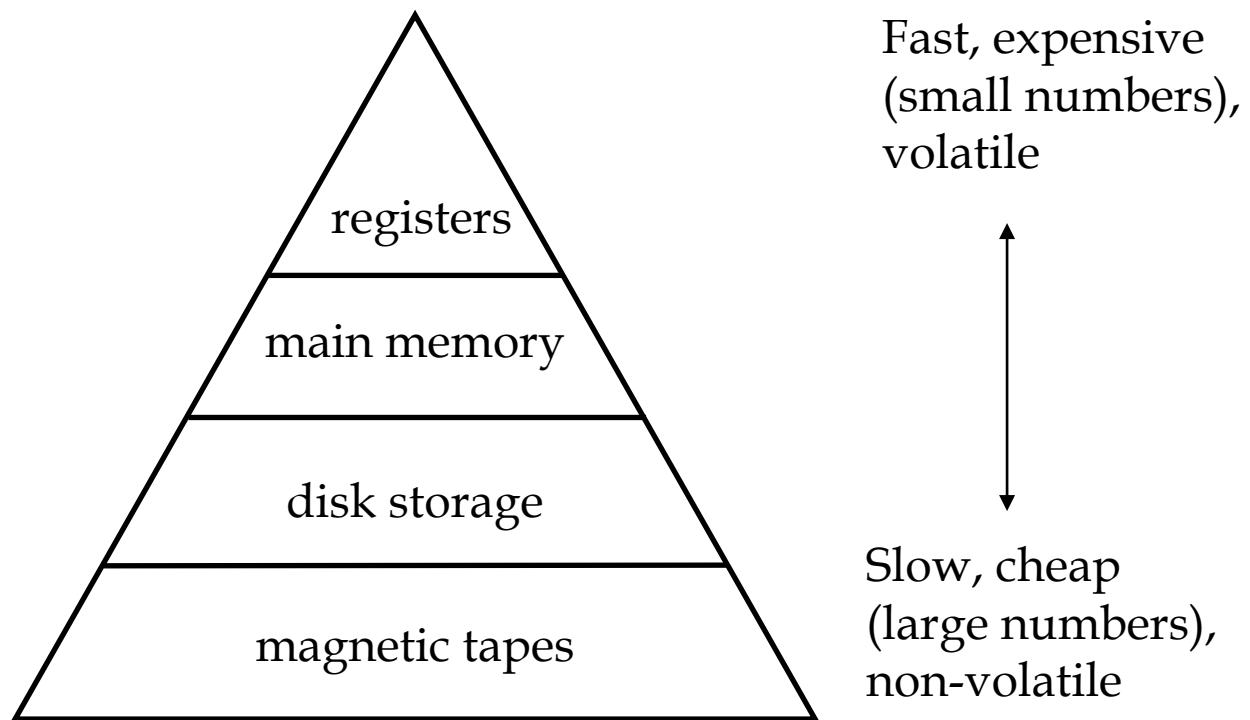

- Desirable properties: fast access, large capacity, economical cost, non-volatile.

- However, most memory devices do not possess all these properties.

# Memory (2/4)

- Memory hierarchy

# Memory (3/4)

- Data transfer

# Memory (4/4)

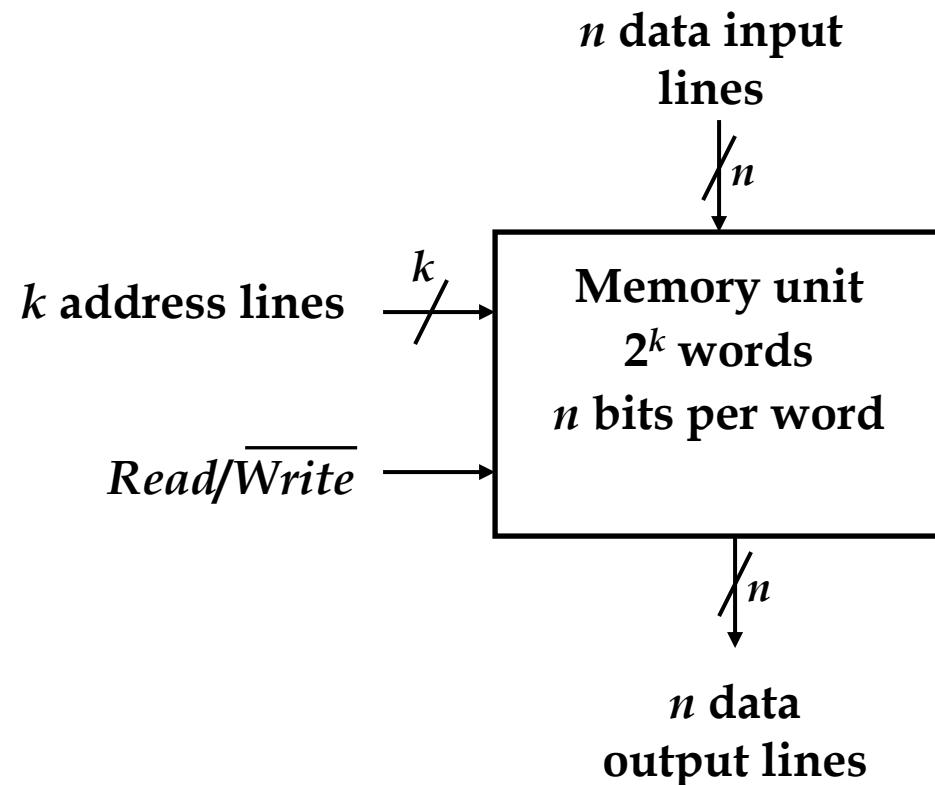

- A memory unit stores binary information in groups of bits called *words*.

- The data consists of  $n$  lines (for  $n$ -bit words). Data input lines provide the information to be stored (*written*) into the memory, while data output lines carry the information out (*read*) from the memory.

- The address consists of  $k$  lines which specify which word (among the  $2^k$  words available) to be selected for reading or writing.

- The control lines *Read* and *Write* (usually combined into a single control line *Read/Write*) specifies the direction of transfer of the data.

# Memory Unit

- Block diagram of a memory unit:

# Read/Write Operations

- **Write** operation:

- Transfers the address of the desired word to the address lines.

- Transfers the data bits (the word) to be stored in memory to the data input lines.

- Activates the *Write* control line (set *Read/Write* to 0).

- **Read** operation:

- Transfers the address of the desired word to the address lines.

- Activates the *Read* control line (set *Read/Write* to 1).

| Memory Enable | <i>Read/Write</i> | Memory Operation |

|---------------|-------------------|------------------|

| 0             | X                 |                  |

| 1             | 0                 |                  |

| 1             | 1                 |                  |

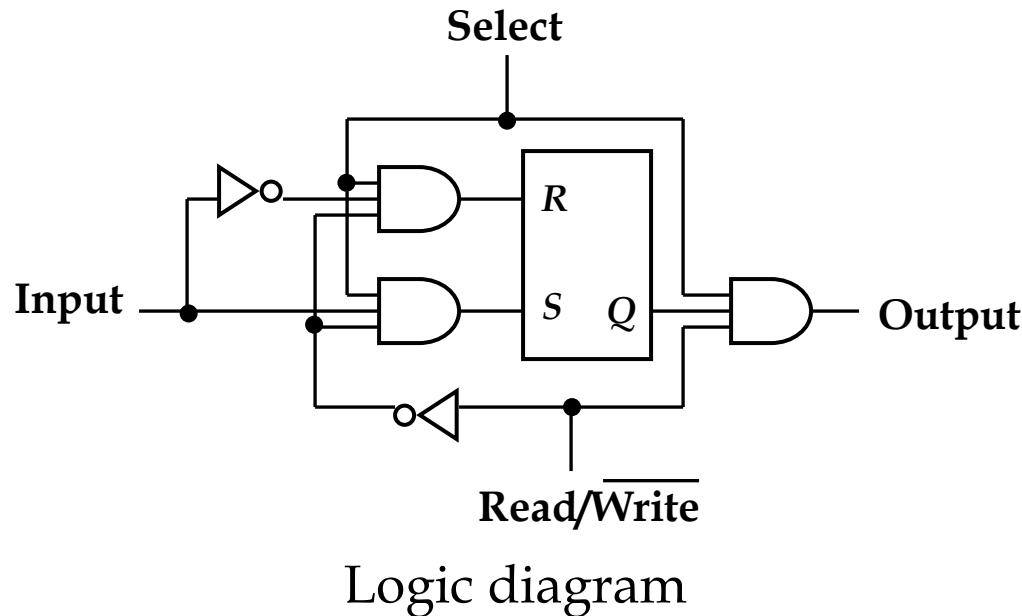

# Memory Cell

- Two types of RAM

- Static RAMs use flip-flops as the memory cells.

- Dynamic RAMs use capacitor charges to represent data. Though simpler in circuitry, they have to be constantly refreshed.

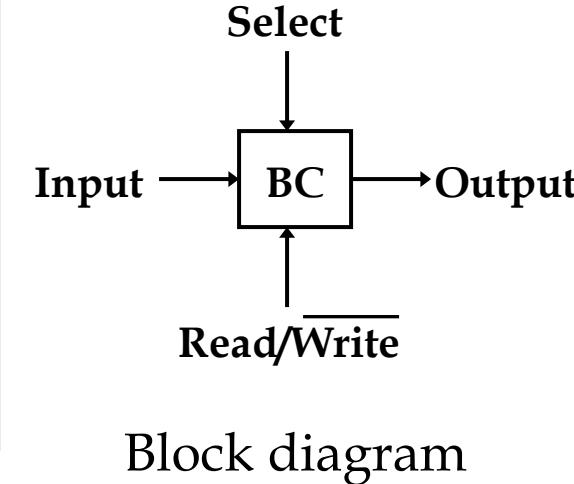

- A single memory cell of the static RAM has the following logic and block diagrams:

Logic diagram

Block diagram

# Memory Arrays (1/4)

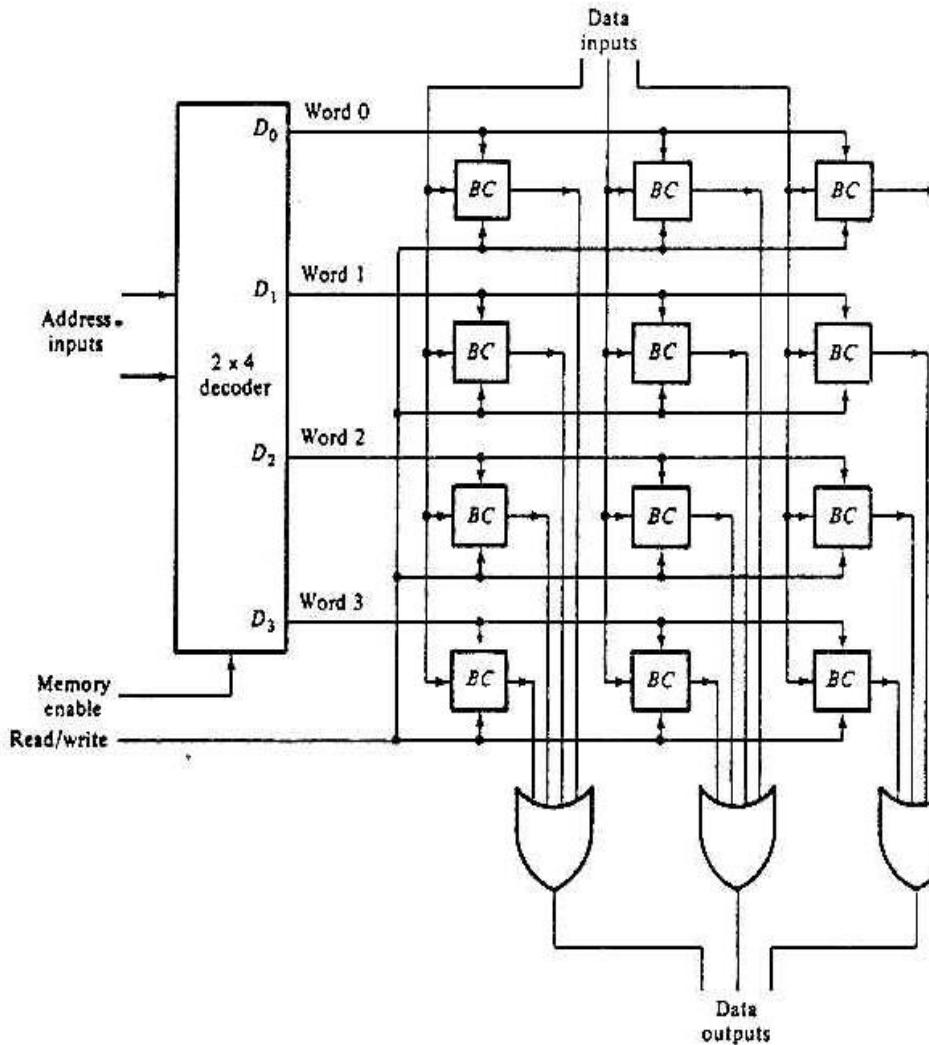

- Logic construction of a  $4 \times 3$  RAM (with decoder and OR gates):

# Memory Arrays (2/4)

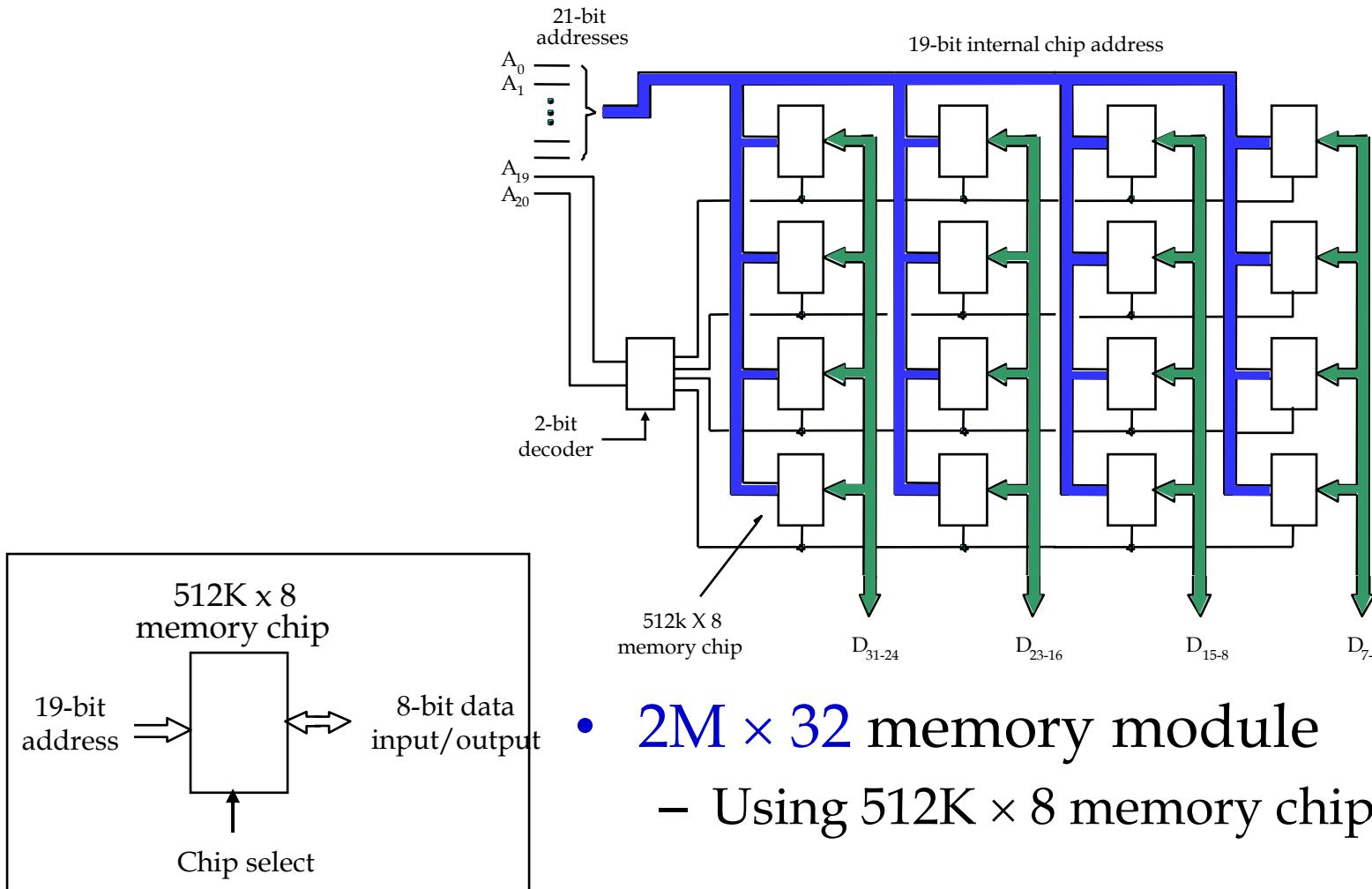

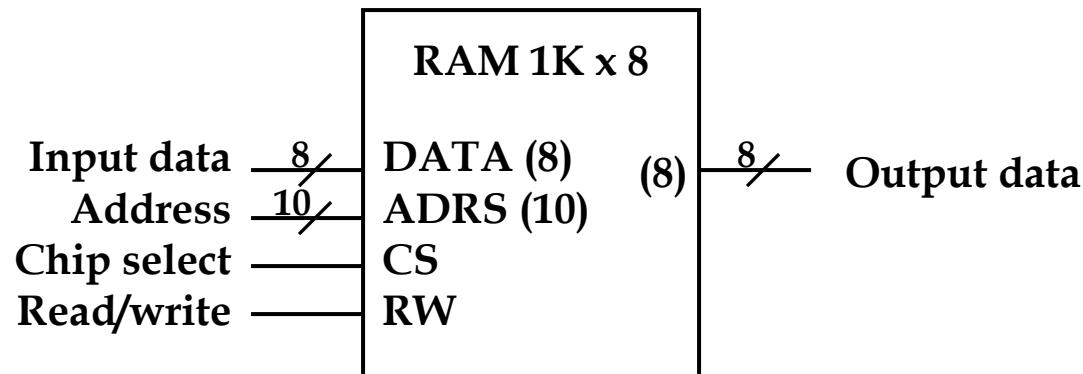

- An array of RAM chips: memory chips are combined to form larger memory.

- A  $1K \times 8$ -bit RAM chip:

Block diagram of a  $1K \times 8$  RAM chip

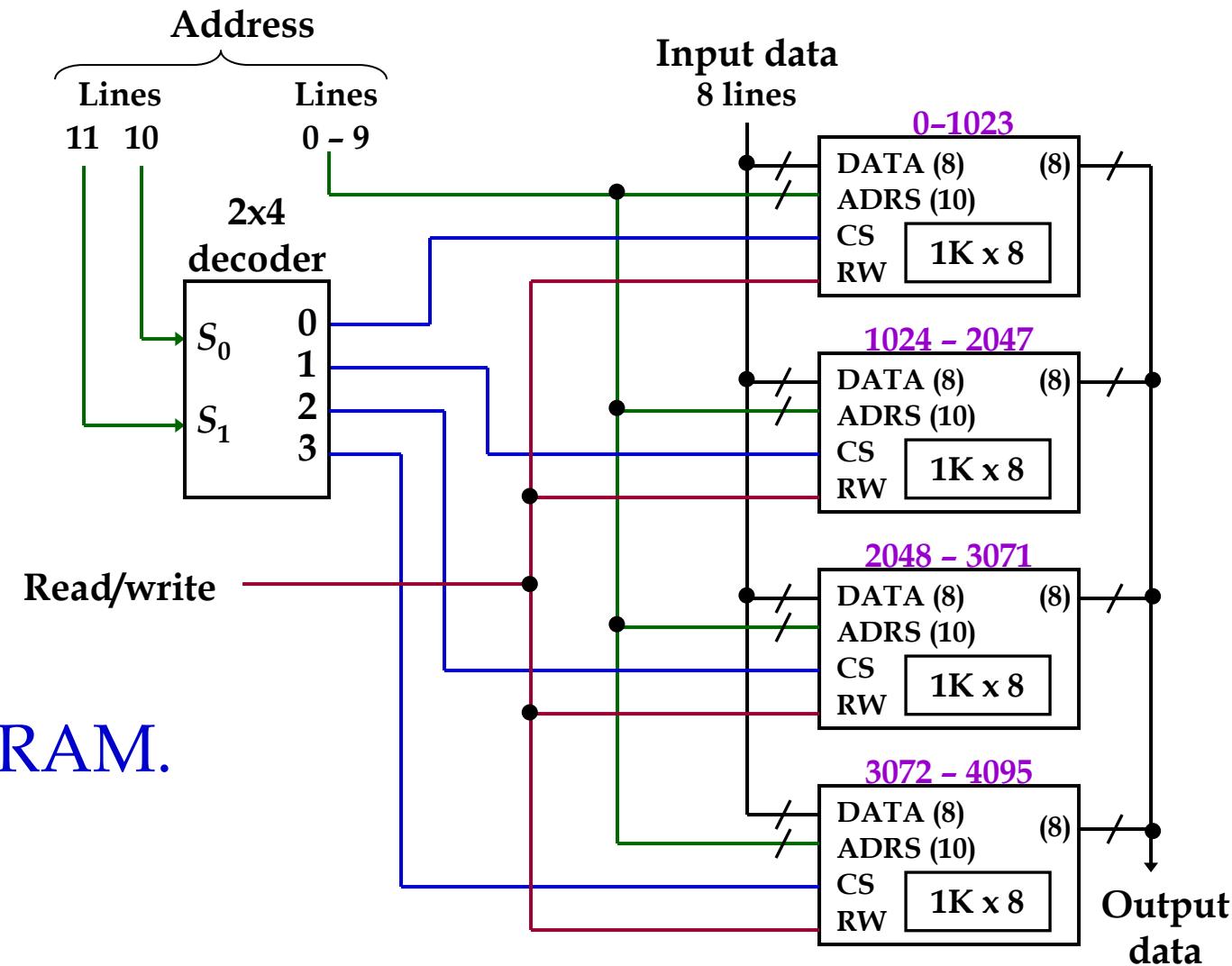

# Memory Arrays (3/4)

# Memory Arrays (4/4)