# **Sequential Logic**

CSIM601251 Instructor: Tim Dosen DDAK Slide By : Erdefi Rakun Fasilkom UI

## Outline

- Memory Elements

- Latches: *S*-*R* Latch, *D* Latch

- Flip-flops: *S*-*R* flip-flop, *D* flip-flop, *J*-*K* flip-flops, *T* flip-flops

- Asynchronous Inputs

- Synchronous Sequential Circuit Analysis

Note: These slides are taken from Aaron Tan's slide

#### Introduction (1/2)

- Two classes of logic circuits

- Combinational

- Sequential

- Combinational Circuit

- Each output depends entirely on the immediate (present) inputs.

• Each output depends on both present inputs and state.

#### Introduction (2/2)

- Two types of sequential circuits:

- Synchronous: outputs change only at specific time

- Asynchronous: outputs change at any time

- Multivibrator: a class of sequential circuits

- Bistable (2 stable states)

- Monostable or one-shot (1 stable state)

- Astable (no stable state)

- Bistable logic devices

- Latches and flip-flops.

- They differ in the methods used for changing their state.

#### Memory Elements (1/3)

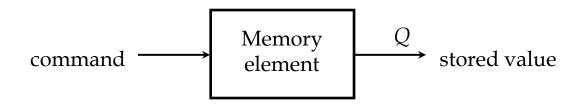

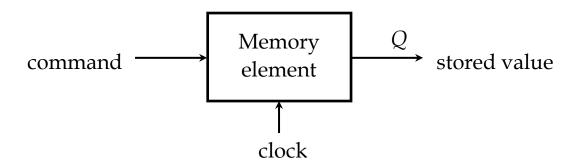

• Memory element: a device which can remember value indefinitely, or change value on command from its inputs.

Characteristic table:

| Command<br>(at time <i>t</i> ) | Q(t) | Q(t+1) |

|--------------------------------|------|--------|

| Set                            | Х    | 1      |

| Reset                          | Х    | 0      |

| Memorise /                     | 0    | 0      |

| No Change                      | 1    | 1      |

*Q*(*t*) or *Q*: current state *Q*(*t*+1) or *Q*<sup>+</sup>: next state

• Memory element with clock.

• Clock is usually a square wave.

#### Memory Elements (3/3)

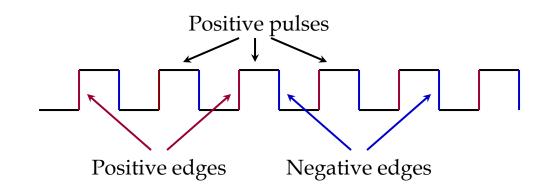

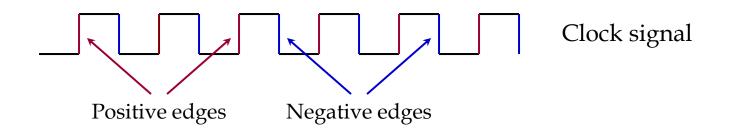

- Two types of triggering/activation

- Pulse-triggered

- Edge-triggered

- Pulse-triggered

- Latches

- ON = 1, OFF = 0

- Edge-triggered

- Flip-flops

- Positive edge-triggered (ON = from 0 to 1; OFF = other time)

- Negative edge-triggered (ON = from 1 to 0; OFF = other time)

Positive pulses

## Outline

- Memory Elements

- Latches: *S*-*R* Latch, *D* Latch

- Flip-flops: *S*-*R* flip-flop, *D* flip-flop, *J*-*K* flip-flops, *T* flip-flops

- Asynchronous Inputs

- Synchronous Sequential Circuit Analysis

Note: These slides are taken from Aaron Tan's slide

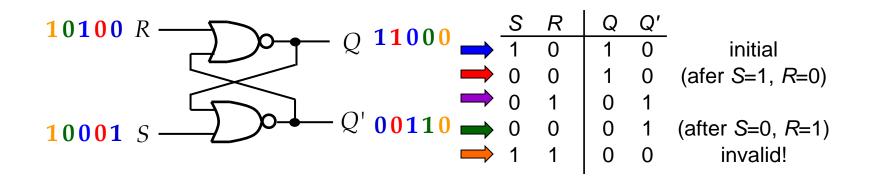

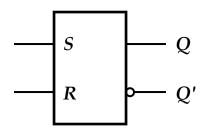

#### **S-R Latch (1/3)**

- Two inputs: *S* and *R*.

- Two complementary outputs: *Q* and *Q*'.

- When Q = HIGH, we say latch is in SET state.

- When Q = LOW, we say latch is in RESET state.

- For active-high input *S*-*R* latch (also known as NOR gate latch)

- R = HIGH and S = LOW  $\rightarrow$  Q becomes LOW (RESET state)

- *S* = HIGH and *R* = LOW  $\rightarrow$  *Q* becomes HIGH (SET state)

- Both *R* and *S* are LOW  $\rightarrow$  No change in output *Q*

- Both *R* and *S* are HIGH →Outputs *Q* and *Q*' are both LOW (invalid!)

- Drawback: invalid condition exists and must be avoided.

• Active-high input *S*-*R* latch:

• Block diagram:

• Characteristic table for active-high input *S-R* latch:

| S | R | Q  | Q' |                                                |

|---|---|----|----|------------------------------------------------|

| 0 | 0 | NC | NC | No change. Latch<br>remained in present state. |

| 1 | 0 | 1  | 0  | Latch SET.                                     |

| 0 | 1 | 0  | 1  | Latch RESET.                                   |

| 1 | 1 | 0  | 0  | Invalid condition.                             |

| S | R | Q(t+1)        |           |   |

|---|---|---------------|-----------|---|

| 0 | 0 | Q(t)          | No change | C |

| 0 | 1 | 0             | Reset     | × |

| 1 | 0 | 1             | Set       |   |

| 1 | 1 | indeterminate |           |   |

$$Q(t+1) = ?$$

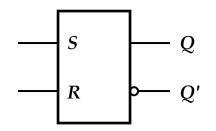

#### Gated S-R Latch

• *S*-*R* latch + *enable input* (*EN*) and 2 NAND gates → a gated *S*-*R* latch.

• Outputs change (if necessary) only when *EN* is high.

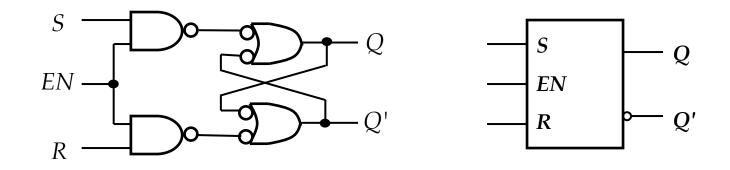

#### Gated D Latch (1/2)

- Make input *R* equal to  $S' \rightarrow \text{gated } D$  latch.

- *D* latch eliminates the undesirable condition of invalid state in the *S*-*R* latch.

#### Gated D Latch (2/2)

- When *EN* is high,

- − D = HIGH → latch is SET

- −  $D = LOW \rightarrow latch is RESET$

- Hence when EN is high, *Q* "follows" the *D* (data) input.

- Characteristic table:

| EN | D | Q(t+1) |           |

|----|---|--------|-----------|

| 1  | 0 | 0      | Reset     |

| 1  | 1 | 1      | Set       |

| 0  | Χ | Q(t)   | No change |

When EN=1, Q(t+1) = ?

## Outline

- Memory Elements

- Latches: *S*-*R* Latch, *D* Latch

- Flip-flops: *S*-*R* flip-flop, *D* flip-flop, *J*-*K* flip-flops, *T* flip-flops

- Asynchronous Inputs

- Synchronous Sequential Circuit Analysis

Note: These slides are taken from Aaron Tan's slide

### Flip-Flops (1/2)

- Flip-flops are synchronous bistable devices.

- Output changes state at a specified point on a triggering input called the clock.

- Change state either at the positive (rising) edge, or at the negative (falling) edge of the clock signal.

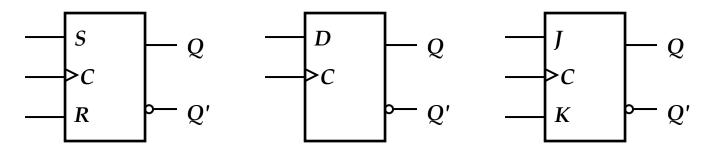

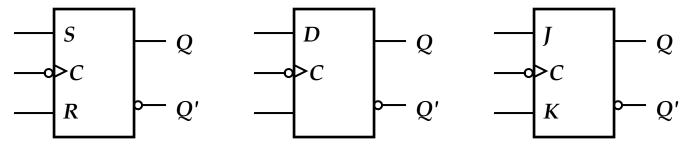

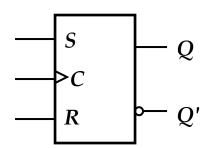

#### Flip-Flops (2/2)

- *S*-*R* flip-flop, *D* flip-flop, and *J*-*K* flip-flop.

- Note the ">" symbol at the clock input.

Positive edge-triggered flip-flops

Negative edge-triggered flip-flops

### S-R Flip-Flop

- *S-R* flip-flop: On the triggering edge of the clock pulse,

- R = HIGH and S = LOW  $\rightarrow$  Q becomes LOW (RESET state)

- *S* = HIGH and *R* = LOW  $\rightarrow$  *Q* becomes HIGH (SET state)

- Both *R* and *S* are LOW  $\rightarrow$  No change in output *Q*

- Both *R* and *S* are HIGH  $\rightarrow$  Invalid!

- Characteristic table of positive edge-triggered *S*-*R* flip-flop:

| S | R | CLK | Q(t+1)      | Comments  |

|---|---|-----|-------------|-----------|

| 0 | 0 | Х   | <i>Q(t)</i> | No change |

| 0 | 1 | 1   | 0           | Reset     |

| 1 | 0 | 1   | 1           | Set       |

| 1 | 1 | 1   | ?           | Invalid   |

X = irrelevant ("don't care")

$\uparrow$  = clock transition LOW to HIGH

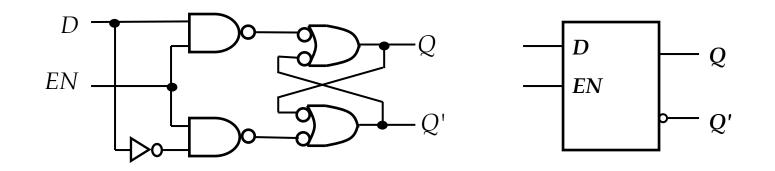

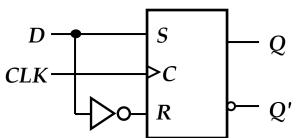

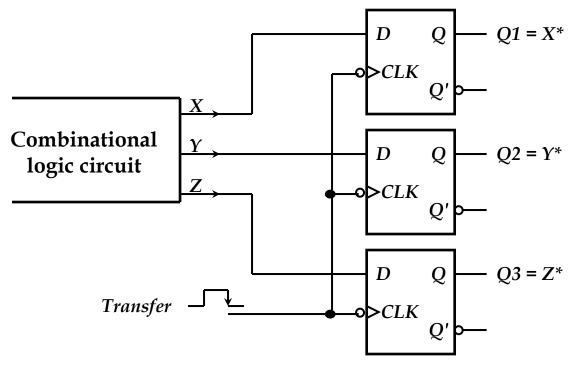

## D Flip-Flop (1/2)

- *D* flip-flop: Single input *D* (data). On the triggering edge of the clock pulse,

- $D = HIGH \rightarrow Q$  becomes HIGH (SET state)

- $D = LOW \rightarrow Q$  becomes LOW (RESET state)

- Hence, *Q* "follows" *D* at the clock edge.

- Convert *S*-*R* flip-flop into a *D* flip-flop: add an inverter.

| D | CLK | Q(t+1) | Comments |

|---|-----|--------|----------|

| 1 | 1   | 1      | Set      |

| 0 | 1   | 0      | Reset    |

A positive edge-triggered D flipflop formed with an S-R flipflop.  $\uparrow$  = clock transition LOW to HIGH

- Application: Parallel data transfer.

- To transfer logic-circuit outputs *X*, *Y*, *Z* to flip-flops *Q*1, *Q*2 and *Q*3 for storage.

\* After occurrence of negative-going transition

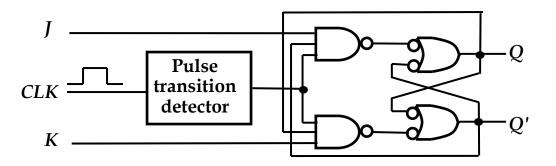

## J-K Flip-Flop (1/2)

- *J-K* flip-flop: *Q* and *Q*' are fed back to the pulse-steering NAND gates.

- No invalid state.

- Include a toggle state

- $J = HIGH and K = LOW \rightarrow Q$  becomes HIGH (SET state)

- K = HIGH and J = LOW  $\rightarrow Q$  becomes LOW (RESET state)

- Both *J* and *K* are LOW  $\rightarrow$  No change in output *Q*

- Both *J* and *K* are HIGH  $\rightarrow$  Toggle

• *J-K* flip-flop circuit:

• Characteristic table:

| J | Κ | CLK        | Q(t+1)      | Comments  |

|---|---|------------|-------------|-----------|

| 0 | 0 | 1          | <i>Q(t)</i> | No change |

| 0 | 1 | 1          | 0           | Reset     |

| 1 | 0 | 1          | 1           | Set       |

| 1 | 1 | $\uparrow$ | Q(t)'       | Toggle    |

*Q*(*t*+1) = ?

| Q | J | Κ | Q(t+1) |

|---|---|---|--------|

| 0 | 0 | 0 | 0      |

| 0 | 0 | 1 | 0      |

| 0 | 1 | 0 | 1      |

| 0 | 1 | 1 | 1      |

| 1 | 0 | 0 | 1      |

| 1 | 0 | 1 | 0      |

| 1 | 1 | 0 | 1      |

| 1 | 1 | 1 | 0      |

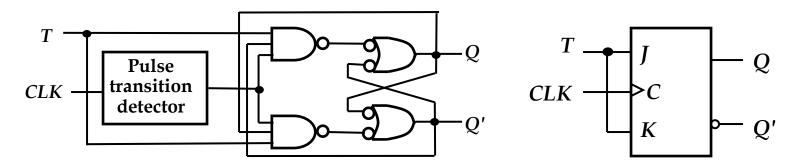

• *T* flip-flop: Single input version of the *J*-*K* flip-flop, formed by tying both inputs together.

• Characteristic table:

| Τ | CLK        | Q(t+1)      | Comments  |

|---|------------|-------------|-----------|

| 0 | 1          | <i>Q(t)</i> | No change |

| 1 | $\uparrow$ | Q(t)'       | Toggle    |

| Q | Τ | Q(t+1) |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 0      |

Q(t+1) = ?

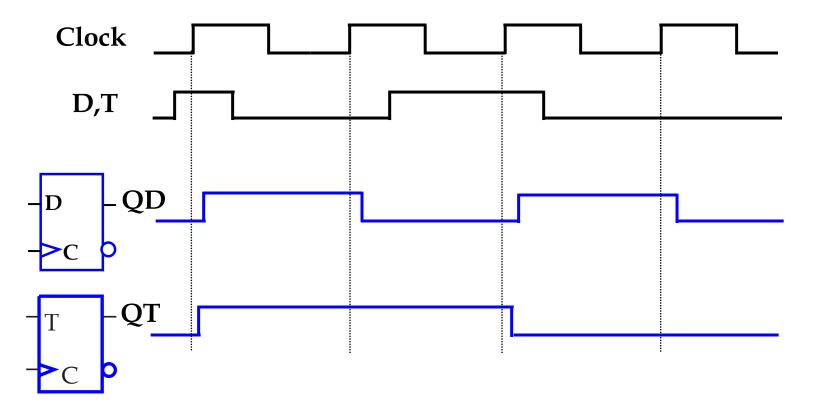

## **Flip-flop Behavior Example**

• Use the characteristic tables to find the output waveforms for the flip-flops shown:

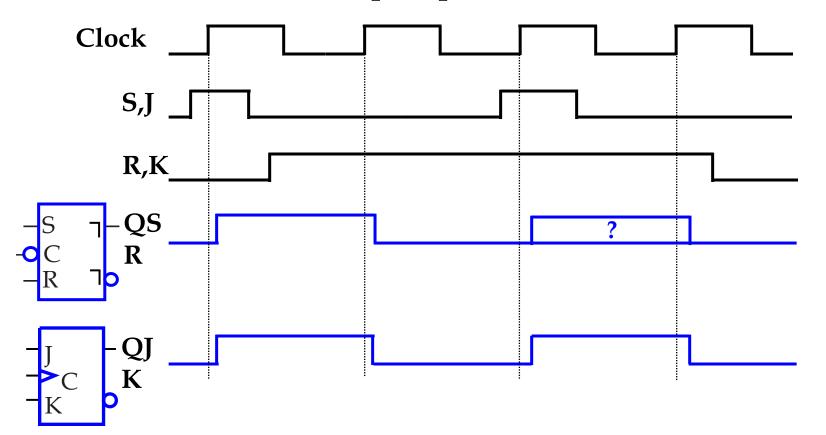

#### Flip-Flop Behavior Example (continued)

• Use the characteristic tables to find the output waveforms for the flip-flops shown:

## Outline

- Memory Elements

- Latches: *S*-*R* Latch, *D* Latch

- Flip-flops: *S*-*R* flip-flop, *D* flip-flop, *J*-*K* flip-flops, *T* flip-flops

- Asynchronous Inputs

- Synchronous Sequential Circuit Analysis

Note: These slides are taken from Aaron Tan's slide

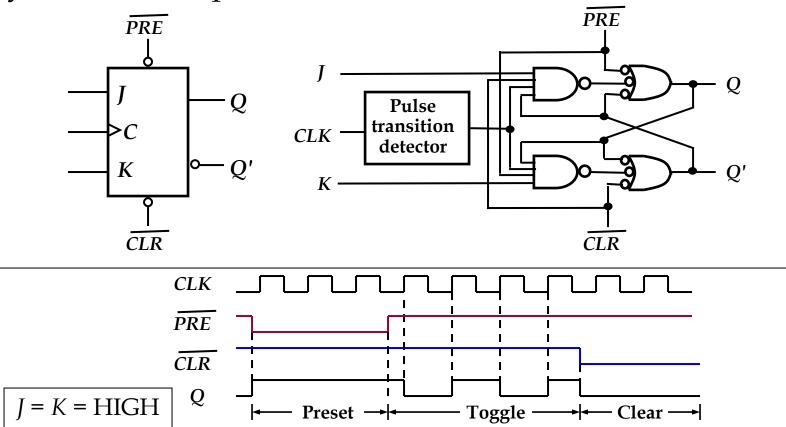

### Asynchronous Inputs (1/2)

- *S*-*R*, *D* and *J*-*K* inputs are synchronous inputs, as data on these inputs are transferred to the flip-flop's output only on the triggered edge of the clock pulse.

- Asynchronous inputs affect the state of the flip-flop independent of the clock; example: *preset* (*PRE*) and *clear* (*CLR*) [or *direct set* (*SD*) and *direct reset* (*RD*)].

- When *PRE*=HIGH, *Q* is <u>immediately</u> set to HIGH.

- When *CLR*=HIGH, *Q* is <u>immediately</u> cleared to LOW.

- Flip-flop in normal operation mode when both *PRE* and *CLR* are LOW.

#### Asynchronous Inputs (2/2)

• A *J*-*K* flip-flop with active-low PRESET and CLEAR asynchronous inputs.

## Outline

- Memory Elements

- Latches: *S*-*R* Latch, *D* Latch

- Flip-flops: *S*-*R* flip-flop, *D* flip-flop, *J*-*K* flip-flops, *T* flip-flops

- Asynchronous Inputs

- Synchronous Sequential Circuit Analysis

Note: These slides are taken from Aaron Tan's slide

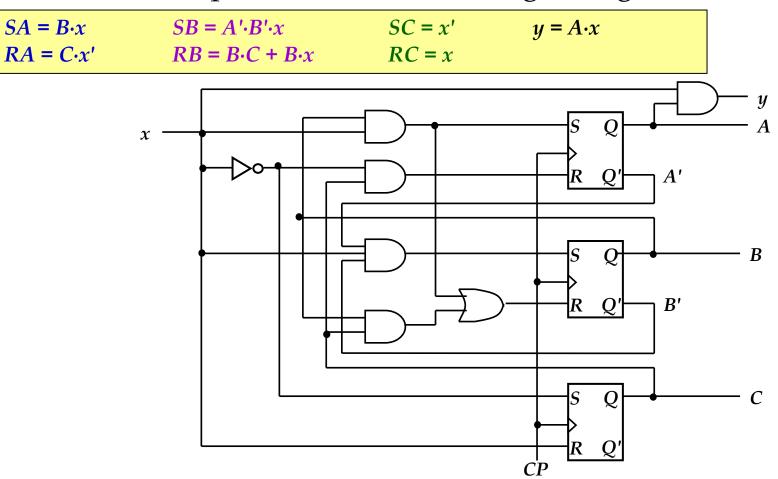

## **Synchronous Sequential Circuits**

- Building blocks: logic gates and flip-flops.

- Flip-flops make up the memory while the gates form one or more combinational subcircuits.

- We have discussed *S*-*R* flip-flop, *J*-*K* flip-flop, *D* flip-flop and *T* flip-flop.

#### **Flip-Flop Characteristic Tables**

• Each type of flip-flop has its own behaviour, shown by its characteristic table.

| J | K | Q(t+1)      | Comments  | - | S | R |

|---|---|-------------|-----------|---|---|---|

| 0 | 0 | <i>Q(t)</i> | No change | _ | 0 | 0 |

| 0 | 1 | 0           | Reset     |   | 0 | 1 |

| 1 | 0 | 1           | Set       |   | 1 | 0 |

| 1 | 1 | Q(t)'       | Toggle    |   | 1 | 1 |

|   | S | R | Q(t+1)      | Comments      |

|---|---|---|-------------|---------------|

|   | 0 | 0 | <i>Q(t)</i> | No change     |

| ( | 0 | 1 | 0           | Reset         |

| 1 | 1 | 0 | 1           | Set           |

| 1 | 1 | 1 | ?           | Unpredictable |

| D | Q(t+1) | _     |

|---|--------|-------|

| 0 | 0      | Reset |

| 1 | 1      | Set   |

| Τ | Q(t+1)      |           |

|---|-------------|-----------|

| 0 | <i>Q(t)</i> | No change |

| 1 | Q(t)'       | Toggle    |

## Sequential Circuits: Analysis (1/7)

- Given a sequential circuit diagram, we can analyze its behaviour by deriving its *state table* and hence its *state diagram*.

- Requires *state equations* to be derived for the flipflop inputs, as well as *output functions* for the circuit outputs other than the flip-flops (if any).

- We use *A*(*t*) and *A*(*t*+1) (or simply *A* and *A*<sup>+</sup>) to represent the present state and next state, respectively, of a flip-flop represented by *A*.

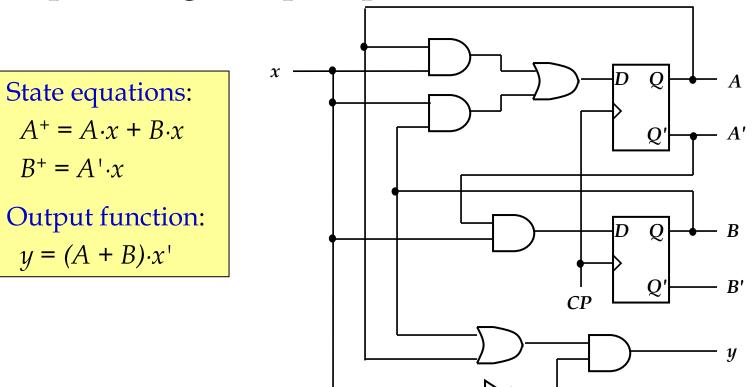

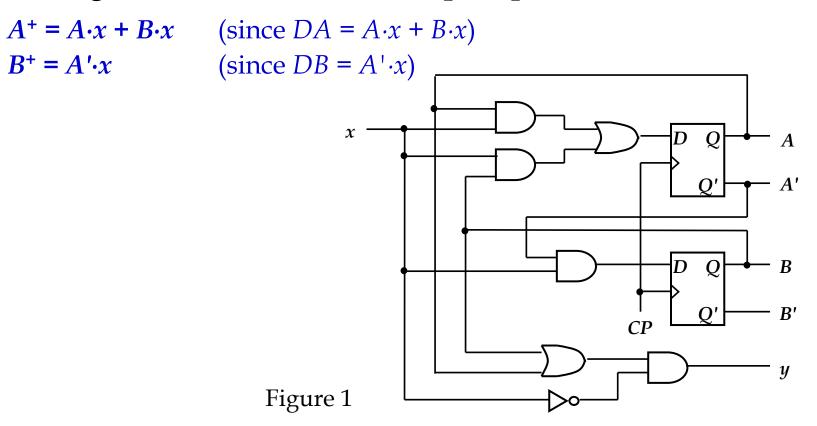

#### Sequential Circuits: Analysis (2/7)

• Example using *D* flip-flops

Figure 1

## Sequential Circuits: Analysis (3/7)

- From the *state equations* and *output function*, we derive the *state table*, consisting of all possible binary combinations of present states and inputs.

- State table

- Similar to truth table.

- Inputs and present state on the left side.

- Outputs and next state on the right side.

- *m* flip-flops and *n* inputs  $\rightarrow 2^{m+n}$  rows.

## Sequential Circuits: Analysis (4/7)

• *State table* for circuit of Figure 1:

| State equations:              |         |   | Output function: |                        |         |               |  |  |

|-------------------------------|---------|---|------------------|------------------------|---------|---------------|--|--|

| $A^+ = A \cdot x + B \cdot x$ |         |   |                  | $y = (A + B) \cdot x'$ |         |               |  |  |

| $B^+ = A' \cdot x$            |         |   |                  |                        |         |               |  |  |

|                               | Present |   |                  | Next                   |         |               |  |  |

|                               | State   |   | Input            | Sta                    | ate     | <u>Output</u> |  |  |

|                               | Α       | В | X                | <b>A</b> <sup>+</sup>  | $B^{+}$ | У             |  |  |

|                               | 0       | 0 | 0                | 0                      | 0       | 0             |  |  |

|                               | 0       | 0 | 1                | 0                      | 1       | 0             |  |  |

|                               | 0       | 1 | 0                | 0                      | 0       | 1             |  |  |

|                               | 0       | 1 | 1                | 1                      | 1       | 0             |  |  |

|                               | 1       | 0 | 0                | 0                      | 0       | 1             |  |  |

|                               | 1       | 0 | 1                | 1                      | 0       | 0             |  |  |

|                               | 1       | 1 | 0                | 0                      | 0       | 1             |  |  |

|                               | 1       | 1 | 1                | 1                      | 0       | 0             |  |  |

### Sequential Circuits: Analysis (5/7)

• Alternative form of state table:

|               | Present<br>State |                  | Inpu |                                             | Next<br>State         |                       | Output      |   |

|---------------|------------------|------------------|------|---------------------------------------------|-----------------------|-----------------------|-------------|---|

|               | Α                | В                | X    | Ā                                           | +                     |                       | у           |   |

| Full table    | 0                | 0                | 0    | (                                           | )                     | 0                     | 0           |   |

|               | 0                | 0                | 1    | (                                           | )                     | 1                     | 0           |   |

|               | 0                | 1                | 0    | (                                           | )                     | 0                     | 1           |   |

|               | 0                | 1                | 1    | 1                                           |                       | 1                     | 0           |   |

|               | 1                | 0                | 0    | (                                           | )                     | 0                     | 1           |   |

|               | 1                | 0                | 1    | 1                                           |                       | 0                     | 0           |   |

|               | 1                | 1                | 0    | (                                           | )                     | 0                     | 1           |   |

|               | 1                | 1                | 1    | -                                           | I                     | 0                     | 0           | _ |

|               | _                | Present<br>State |      | t Next State                                |                       |                       | Output      |   |

| Compact table |                  |                  |      | <i>x</i> =0 <i>x</i> =1                     |                       | <i>x</i> =0           | <i>x</i> =1 |   |

| Compact table |                  | AB               |      | <b>A</b> <sup>+</sup> <b>B</b> <sup>+</sup> | <b>A</b> <sup>+</sup> | <b>B</b> <sup>+</sup> | У           | У |

|               |                  | 00               |      | 00                                          | 0                     | 1                     | 0           | 0 |

|               |                  | 01               |      | 00                                          | 1                     | 1                     | 1           | 0 |

|               |                  | 10               |      | 00                                          | 1                     | 0                     | 1           | 0 |

|               |                  | 11               |      | 00                                          | 1                     | 0                     | 1           | 0 |

# Sequential Circuits: Analysis (6/7)

- From the *state table*, we can draw the *state diagram*.

- State diagram

- Each state is denoted by a circle.

- Each arrow (between two circles) denotes a transition of the sequential circuit (a row in state table).

- A label of the form *a/b* is attached to each arrow where *a* (if there is one) denotes the inputs while *b* (if there is one) denotes the outputs of the circuit in that transition.

- Each combination of the flip-flop values represents a state. Hence, *m* flip-flops  $\rightarrow$  up to 2<sup>*m*</sup> states.

# Sequential Circuits: Analysis (7/7)

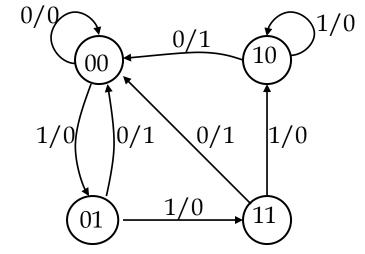

• **State diagram** of the circuit of Figure 1:

| Present | Next                                        | State                                       | Output      |             |  |  |  |

|---------|---------------------------------------------|---------------------------------------------|-------------|-------------|--|--|--|

| State   | <i>x</i> =0                                 | <i>x</i> =1                                 | <i>x</i> =0 | <i>x</i> =1 |  |  |  |

| AB      | <b>A</b> <sup>+</sup> <b>B</b> <sup>+</sup> | <i>A</i> <sup>+</sup> <i>B</i> <sup>+</sup> | У           | У           |  |  |  |

| 00      | 00                                          | 01                                          | 0           | 0           |  |  |  |

| 01      | 00                                          | 11                                          | 1           | 0           |  |  |  |

| 10      | 00                                          | 10                                          | 1           | 0           |  |  |  |

| 11      | 00                                          | 10                                          | 1           | 0           |  |  |  |

JE!

# Flip-Flop Input Function (1/3)

• The outputs of a sequential circuit are functions of the present states of the flip-flops and the inputs. These are described algebraically by the *circuit output functions*.

- In Figure 1:  $y = (A + B) \cdot x'$

- The part of the circuit that generates inputs to the flipflops are described algebraically by the *flip-flop input functions* (or *flip-flop input equations*).

- The flip-flop input functions determine the next state generation.

- From the flip-flop input functions and the characteristic tables of the flip-flops, we obtain the next states of the flip-flops.

### Flip-Flop Input Function (2/3)

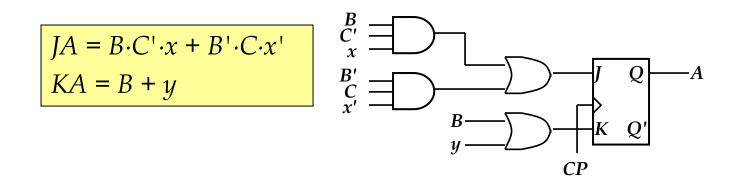

- Example: circuit with a *JK* flip-flop.

- We use 2 letters to denote each flip-flop input: the first letter denotes the input of the flip-flop (*J* or *K* for *J*-*K* flip-flop, *S* or *R* for *S*-*R* flip-flop, *D* for *D* flip-flop, *T* for *T* flip-flop) and the second letter denotes the name of the flip-flop.

# Flip-Flop Input Function (3/3)

• In Figure 1, we obtain the following state equations by observing that *Q*<sup>+</sup> = *DQ* for a *D* flip-flop:

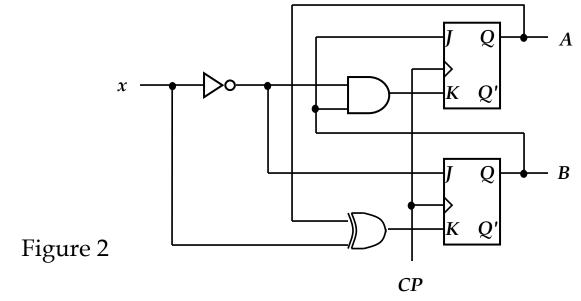

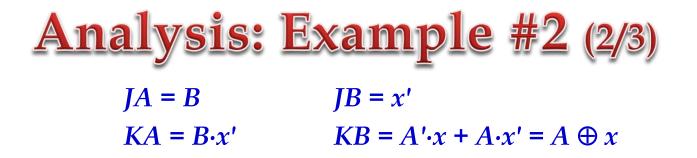

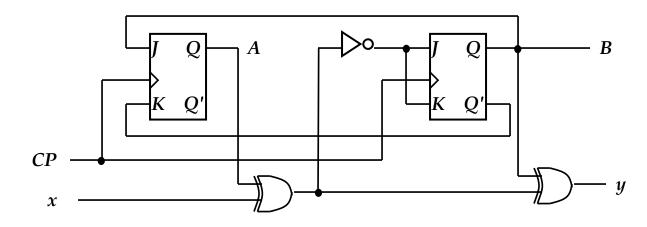

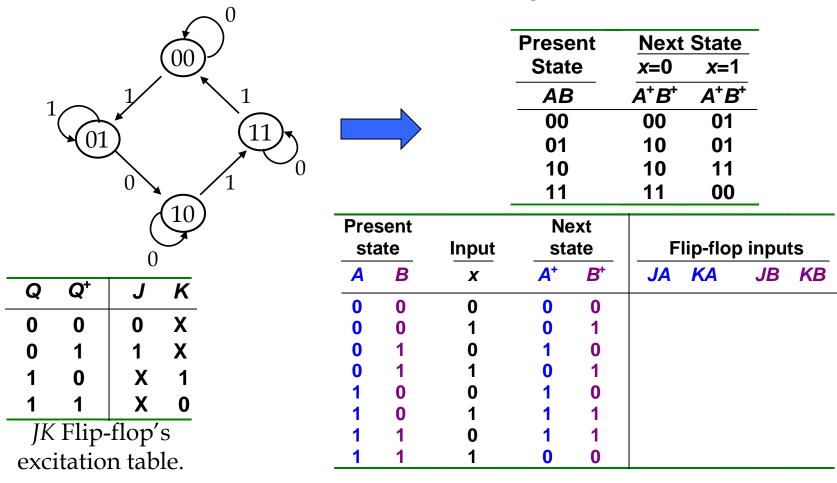

#### Analysis: Example #2 (1/3)

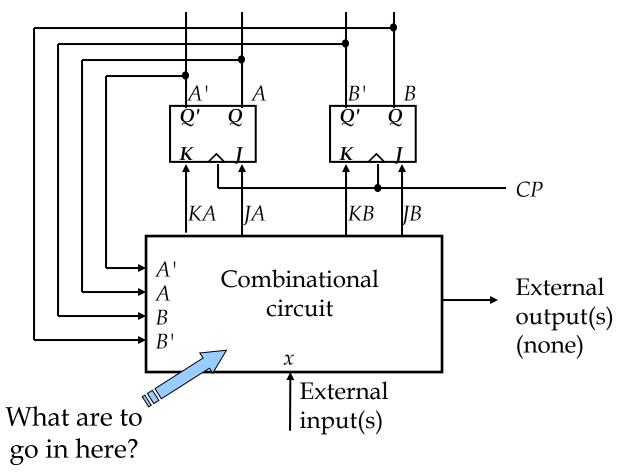

• Given Figure 2, a sequential circuit with two *J*-*K* flip-flops *A* and *B*, and one input *x*.

Obtain the flip-flop input functions from the circuit:

JA = BJB = x' $KA = B \cdot x'$  $KB = A' \cdot x + A \cdot x' = A \oplus x$

Fill the state table using the above functions, knowing the characteristics of the flip-flops used.

| J | Κ | Q(t+1) | Comments  |     |      |       |                       |                       |    |        |        |     |

|---|---|--------|-----------|-----|------|-------|-----------------------|-----------------------|----|--------|--------|-----|

| 0 | 0 | Q(t)   | No change | Pre | sent |       | Ne                    | ext                   |    |        |        |     |

| 0 | 1 | 0      | Reset     | sta | ate  | Input | sta                   | ate                   | Fl | ip-flo | p inpu | Its |

| 1 | 0 | 1      | Set       | A   | В    | X     | <b>A</b> <sup>+</sup> | <b>B</b> <sup>+</sup> | JA | KA     | JB     | KB  |

| 1 | 1 | Q(t)'  | Toggle    | - 0 | 0    | 0     | -                     | -                     |    | 0      | 1      |     |

|   |   |        |           | - 0 | U    | U     |                       |                       | 0  | U      |        | 0   |

|   |   |        |           | 0   | 0    | 1     |                       |                       | 0  | 0      | 0      | 1   |

|   |   |        |           | 0   | 1    | 0     |                       |                       | 1  | 1      | 1      | 0   |

|   |   |        |           | 0   | 1    | 1     |                       |                       | 1  | 0      | 0      | 1   |

|   |   |        |           | 1   | 0    | 0     |                       |                       | 0  | 0      | 1      | 1   |

|   |   |        |           | 1   | 0    | 1     |                       |                       | 0  | 0      | 0      | 0   |

|   |   |        |           | 1   | 1    | 0     |                       |                       | 1  | 1      | 1      | 1   |

|   |   |        |           | 1   | 1    | 1     |                       |                       | 1  | 0      | 0      | 0   |

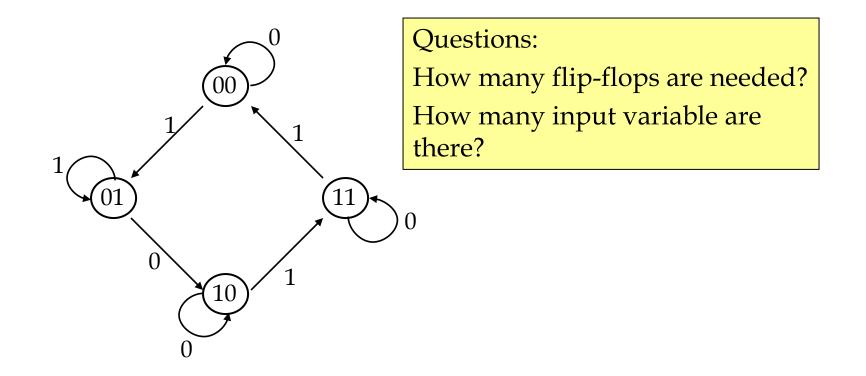

#### Analysis: Example #2 (3/3)

• Draw the state diagram from the state table.

| Present |     |              | Ne                    | ext                   |    |                  |    |    |  |  |  |  |

|---------|-----|--------------|-----------------------|-----------------------|----|------------------|----|----|--|--|--|--|

| sta     | ate | <u>Input</u> | sta                   | ate                   | FI | Flip-flop inputs |    |    |  |  |  |  |

| Α       | В   | X            | <b>A</b> <sup>+</sup> | <b>B</b> <sup>+</sup> | JA | KA               | JB | KB |  |  |  |  |

| 0       | 0   | 0            |                       |                       | 0  | 0                | 1  | 0  |  |  |  |  |

| 0       | 0   | 1            |                       |                       | 0  | 0                | 0  | 1  |  |  |  |  |

| 0       | 1   | 0            |                       |                       | 1  | 1                | 1  | 0  |  |  |  |  |

| 0       | 1   | 1            |                       |                       | 1  | 0                | 0  | 1  |  |  |  |  |

| 1       | 0   | 0            |                       |                       | 0  | 0                | 1  | 1  |  |  |  |  |

| 1       | 0   | 1            |                       |                       | 0  | 0                | 0  | 0  |  |  |  |  |

| 1       | 1   | 0            |                       |                       | 1  | 1                | 1  | 1  |  |  |  |  |

| 1       | 1   | 1            |                       |                       | 1  | 0                | 0  | 0  |  |  |  |  |

#### Analysis: Example #3 (1/3)

• Derive the state table and state diagram of this circuit.

Figure 3

• Flip-flop input functions:

JA = B $JB = KB = (A \oplus x)' = A \cdot x + A' \cdot x'$ KA = B'

## Analysis: Example #3 (2/3)

• Flip-flop input functions:

KA = B'

$JA = B \qquad \qquad JB = KB = (A \oplus x)' = A \cdot x + A' \cdot x'$

• State table:

| Pres         | sent |              | N                     | ext                   |               |     |        |               |     |

|--------------|------|--------------|-----------------------|-----------------------|---------------|-----|--------|---------------|-----|

| <u>state</u> |      | <u>Input</u> | st                    | ate                   | <u>Output</u> | Fli | ip-flo | <u>ว inpเ</u> | ıts |

| Α            | B    | X            | <b>A</b> <sup>+</sup> | <b>B</b> <sup>+</sup> | У             | JA  | KA     | JB            | KE  |

| 0            | 0    | 0            |                       |                       | 0             | 0   | 1      | 1             | 1   |

| 0            | 0    | 1            |                       |                       | 1             | 0   | 1      | 0             | 0   |

| 0            | 1    | 0            |                       |                       | 1             | 1   | 0      | 1             | 1   |

| 0            | 1    | 1            |                       |                       | 0             | 1   | 0      | 0             | 0   |

| 1            | 0    | 0            |                       |                       | 1             | 0   | 1      | 0             | 0   |

| 1            | 0    | 1            |                       |                       | 0             | 0   | 1      | 1             | 1   |

| 1            | 1    | 0            |                       |                       | 0             | 1   | 0      | 0             | 0   |

| 1            | 1    | 1            |                       | v                     | 1             | 1   | 0      | 1             | 1   |

# Analysis: Example #3 (3/3)

• State diagram:

| Preser | nt           | Next      |               |    |                     |               |     |  |

|--------|--------------|-----------|---------------|----|---------------------|---------------|-----|--|

| state  | <u>Input</u> | state     | <u>Output</u> | FI | ip-flo <sub>l</sub> | <u>ρ inpι</u> | uts |  |

| A E    | 3 x          | $A^+ B^+$ | У             | JA | KA                  | JB            | KE  |  |

| 0 0    | 0            |           | 0             | 0  | 1                   | 1             | 1   |  |

| 0 0    | ) 1          |           | 1             | 0  | 1                   | 0             | 0   |  |

| 0 1    | 0            |           | 1             | 1  | 0                   | 1             | 1   |  |

| 0 1    | 1            |           | 0             | 1  | 0                   | 0             | 0   |  |

| 1 0    | 0            |           | 1             | 0  | 1                   | 0             | 0   |  |

| 1 0    | ) 1          |           | 0             | 0  | 1                   | 1             | 1   |  |

| 1 1    | 0            |           | 0             | 1  | 0                   | 0             | 0   |  |

| 1 1    | 1            |           | 1             | 1  | 0                   | 1             | 1   |  |

|        |              |           |               |    |                     |               |     |  |

## Flip-Flop Excitation Tables (1/2)

- *Analysis*: Starting from a circuit diagram, derive the state table or state diagram.

- *Design*: Starting from a set of specifications (in the form of state equations, state table, or state diagram), derive the logic circuit.

- *Characteristic tables* are used in analysis.

- *Excitation tables* are used in design.

# Flip-Flop Excitation Tables (2/2)

\_

• *Excitation tables*: given the required transition from present state to next state, determine the flip-flop input(s).

| Q | $Q^{+}$ | J      | K |   | Q | Q | -                   | S | R        |

|---|---------|--------|---|---|---|---|---------------------|---|----------|

| 0 | 0       | 0      | Χ | - | 0 | 0 |                     | 0 | Χ        |

| 0 | 1       | 1      | Χ |   | 0 | 1 |                     | 1 | 0        |

| 1 | 0       | X      | 1 |   | 1 | 0 |                     | 0 | 1        |

| 1 | 1       | X      | 0 |   | 1 | 1 |                     | Χ | 0        |

| Q |         | p-flop | _ |   |   | Q | Elip-:<br><b>Q⁺</b> |   | <b>T</b> |

| 0 |         | 0      | - |   |   | 0 | 0                   |   | 0        |

| 0 | 1       | 1      |   |   |   | 0 | 1                   |   | 1        |

| 1 | 0       | 0      |   |   |   | 1 | 0                   |   | 1        |

| 1 | 1       | 1      |   |   |   | 1 | 1                   |   | 0        |

| D |         |        | _ |   |   |   |                     |   |          |

# **Sequential Circuits: Design**

- Design procedure:

- Start with circuit specifications description of circuit behaviour, usually a state diagram or state table.

- Derive the state table.

- Perform state reduction if necessary.

- Perform state assignment.

- Determine number of flip-flops and label them.

- Choose the type of flip-flop to be used.

- Derive circuit excitation and output tables from the state table.

- Derive circuit output functions and flip-flop input functions.

- Draw the logic diagram.

## Design: Example #1 (1/5)

• Given the following state diagram, design the sequential circuit using *JK* flip-flops.

## Design: Example #1 (2/5)

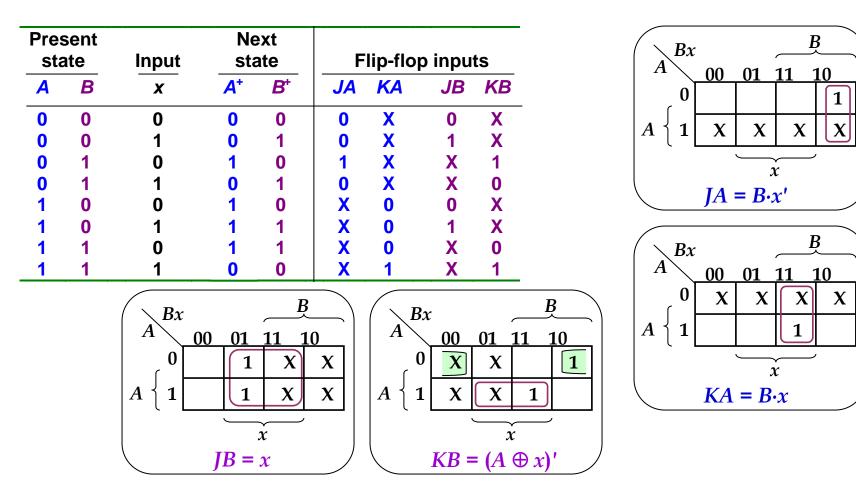

• Circuit state/excitation table, using *JK* flip-flops.

## Design: Example #1 (3/5)

• Block diagram.

#### Design: Example #1 (4/5)

• From state table, get flip-flop input functions.

## Design: Example #1 (5/5)

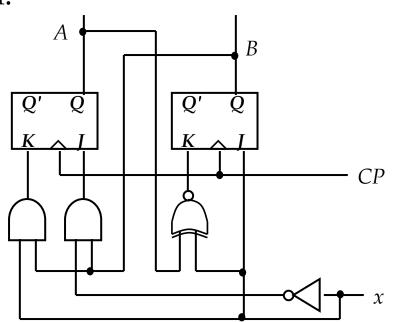

- Flip-flop input functions:  $JA = B \cdot x'$  JB = x

- $KA = B \cdot x$   $KB = (A \oplus x)'$

- Logic diagram:

## Design: Example #2 (1/3)

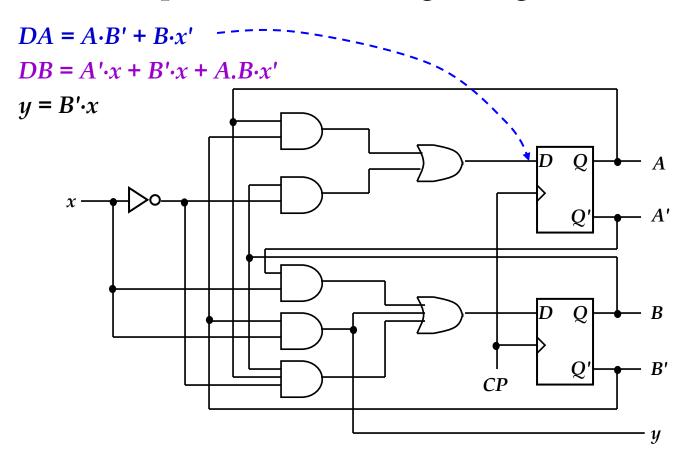

• Using *D* flip-flops, design the circuit based on the state table below. (Exercise: Design it using *JK* flip-flops.)

| Present<br>state<br>A B |   | Input |                       | ext<br>ate            | Output |  |  |

|-------------------------|---|-------|-----------------------|-----------------------|--------|--|--|

|                         |   | X     | <b>A</b> <sup>+</sup> | <b>B</b> <sup>+</sup> | У      |  |  |

| 0                       | 0 | 0     | 0                     | 0                     | 0      |  |  |

| 0                       | 0 | 1     | 0                     | 1                     | 1      |  |  |

| 0                       | 1 | 0     | 1                     | 0                     | 0      |  |  |

| 0                       | 1 | 1     | 0                     | 1                     | 0      |  |  |

| 1                       | 0 | 0     | 1                     | 0                     | 0      |  |  |

| 1                       | 0 | 1     | 1                     | 1                     | 1      |  |  |

| 1                       | 1 | 0     | 1                     | 1                     | 0      |  |  |

| 1                       | 1 | 1     | 0                     | 0                     | 0      |  |  |

## Design: Example #2 (2/3)

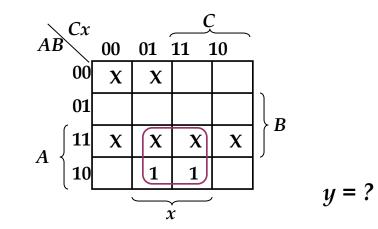

• Determine expressions for flip-flop inputs and the circuit

• From derived expressions, draw logic diagram:

## Design: Example #3 (1/4)

• Design involving unused states.

| P   | rese                                             | nt    |          |            | Next  | :  |    |                  |    |    |    |          |   |        |   |

|-----|--------------------------------------------------|-------|----------|------------|-------|----|----|------------------|----|----|----|----------|---|--------|---|

|     | state                                            | 9     | Input    |            | state |    |    | Flip-flop inputs |    |    |    |          |   | Output |   |

| A   | В                                                | С     | X        | <b>A</b> ⁺ | B+    | C⁺ | SA | RA               | SB | RB | SC | RC       |   | У      |   |

| 0   | 0                                                | 1     | 0        | 0          | 0     | 1  | 0  | X                | 0  | Х  | Х  | 0        |   | 0      |   |

| 0   | 0                                                | 1     | 1        | 0          | 1     | 0  | 0  | X                | 1  | 0  | 0  | 1        |   | 0      |   |

| 0   | 1                                                | 0     | 0        | 0          | 1     | 1  | 0  | X                | Х  | 0  | 1  | 0        |   | 0      |   |

| 0   | 1                                                | 0     | 1        | 1          | 0     | 0  | 1  | 0                | 0  | 1  | 0  | Х        |   | 0      |   |

| 0   | 1                                                | 1     | 0        | 0          | 0     | 1  | 0  | X                | 0  | 1  | Х  | 0        |   | 0      |   |

| 0   | 1                                                | 1     | 1        | 1          | 0     | 0  | 1  | 0                | 0  | 1  | 0  | 1        |   | 0      |   |

| 1   | 0                                                | 0     | 0        | 1          | 0     | 1  | X  | 0                | 0  | Х  | 1  | 0        |   | 0      |   |

| 1   | 0                                                | 0     | 1        | 1          | 0     | 0  | X  | 0                | 0  | Х  | 0  | Х        | - | 1      |   |

| 1   | 0                                                | 1     | 0        | 0          | 0     | 1  | 0  | 1                | 0  | Х  | Х  | 0        | - | 0      |   |

| 1   | 0                                                | 1     | 1        | 1          | 0     | 0  | X  | 0                | 0  | Х  | 0  | 1        |   | 1      |   |

|     | Given these Derive these Are there of unused sta |       |          |            |       |    |    |                  |    |    |    |          |   |        |   |

| Unu | sec                                              | l sta | ate 000: |            |       |    |    |                  |    |    |    |          |   |        | _ |

| 0   | 0                                                | 0     | 0        | X          | ( X   | X  | X  | X                | X  | X  |    | <b>(</b> | X | X      |   |

| 0   | 0                                                | 0     | 1        | X          | X     | X  | X  | X                | Х  | X  |    | (        | Χ | Х      | _ |

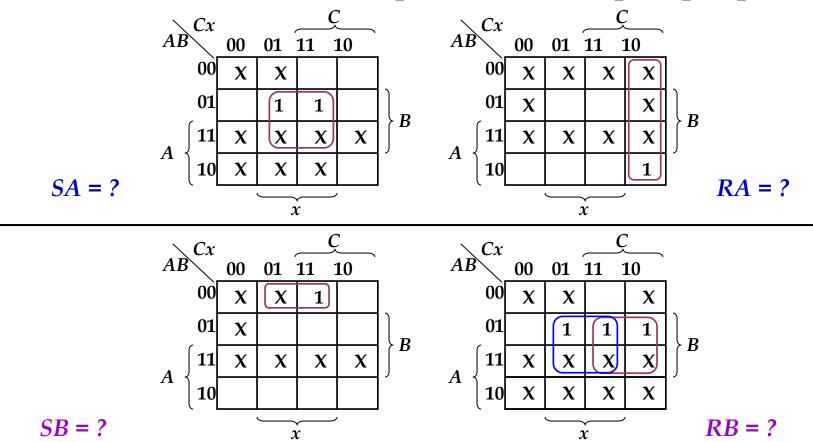

#### Design: Example #3 (2/4)

• From state table, obtain expressions for flip-flop inputs.

#### Design: Example #3 (3/4)

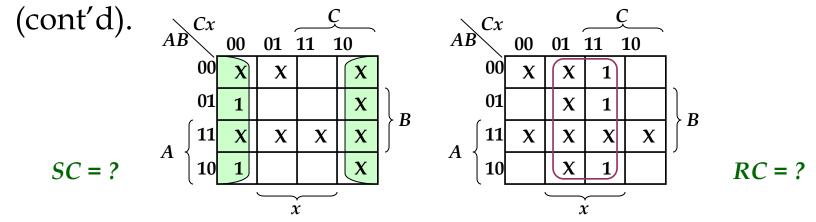

• From state table, obtain expressions for flip-flop inputs

## Design: Example #3 (4/4)

• From derived expressions, draw the logic diagram: